用裸芯片组装以降低成本 - 与 Micross 合作的产品与服务

1.节约成本

使用裸芯片取代传统封装芯片装配快速发展,尤其是在亚洲。在要求高密度和可以获得批量化裸芯片的地方,裸芯片都得到大批量应用。可以降低成本的所属范畴包括基板,装配 ,测试系统,设备使用,返工和提高产品的价值。另外,裸芯片产品的成本一般低于同等级的封装芯片。带凸点的裸芯片和倒装片工艺使工序简化,装配步骤的减少使装配流程更 加流畅。裸芯片的这些优点使现有成熟产品的集成度更高一级,减少成本的同时增加这些产品每平方面积的功能性。此外,这些性能的改善并不需要额外的支出。为系统封装SIP而 集成裸芯片的解决方案比常规的封装方法和SOC方法更具优势,因为产品设计周期要求不断缩短,产品及时到达市场变得日趋重要,用于SIP的裸芯片迎合了设计者的需要并得到大 量应用。下面是当前常用装配工艺的基准成本对比方块图。

| PROCESS FLOW | |||||||

| Estimated Manufacturing Cost for a 20 Lead device* | EQUIPMENT COST | HERMETIC | STD PLASTIC | FLIP CSP | COB | SOLDER FLIP | GOLD BUMP-FLIP |

| WAFER SUPPLIER | |||||||

| FAB | $0.10 | $0.10 | $0.10 | $0.10 | $0.10 | $0.10 | |

| PROBE/TEST | $1M | $0.02 | $0.02 | $0.02 | $0.02 | $0.02 | $0.02 |

| BUMP | $250K | $0.01 | |||||

| PACKAGING | |||||||

| BUMP | $250K | $0.01 | $0.01 | ||||

| SAW AND MOUNT | $500K | $0.01 | $0.01 | $0.01 | $0.01 | $0.01 | $0.01 |

| PACKAGE | $2.00 | $0.05 | $0.02 | ||||

| DIE ATTACH | $100K | $0.10 | $0.05 | $0.10 | |||

| WIRE BOND | $250K | $0.20 | $0.02 | ||||

| ENCAP | $100K | $2.00 | $0.02 | $0.02 | |||

| TEST | $1M | $0.05 | $0.05 | $0.05 | $0.05 | ||

| PCB ASSEMBLER | |||||||

| PCB @ $/sq.cm | $0.2 | 0.400 | 0.400 | 0.050 | 0.018 | 0.002 | 0.002 |

| PRINT & PLACE | $1M | $0.05 | $0.05 | $0.05 | $0.05 | $0.05 | $0.05 |

| REFLOW/CURE | $100K | $0.01 | $0.01 | $0.01 | $0.01 | $0.01 | $0.01 |

| WIRE BOND | $250K | $0.20 | |||||

| TOTAL DEVICE COST | $4.94 | $0.78 | $0.44 | $0.41 | $0.20 | $0.25 | |

| ADDITIONAL INVESTMENT for PCB ASSEMBLER | $ 250,000 | $ 100,000 | $ 100,000 | ||||

| COST FOR 1 MILLION COMPONENTS | $4.94 | $0.78 | $0.44 | $0.66 | $0.30 | $0.35 | |

上面的数据基于如下假设:

1. 每平方分米PCB板的成本40美金

2. 所有成本都基于1KK的元件数量

3. 成本模式依管芯含铅量的高低而有轻微的变动,但是每种封装方式的总体成本是基本相似的。

请联络我们,我们很乐意基于您的个案研究相应的成本模型

综上所述,使用裸芯片装配的成本优势分析如下

更高的集成度

减少基板尺寸和成本

减少装配生产的工艺成本

更及时到达市场

更高的产品价值

相同面积上裸芯片提供更多的性能和重量的减轻

2. 如何建立裸芯片装配生产线——要点:

首先,从数量上来说,使用裸芯片装配后产品的生产成本是否会降低?参见上面的矩阵图。其次,有没有其他的技术因素要使用裸芯片?是否要求更小,更轻,散热更佳或是有些器件需要运行更快速?

客户需要根据最适合产品电路的技术作出决定。例如,在小批量,或是较大的温度范围,最佳首选是板上直接贴装。在大批量时的最佳首选是倒装片。主要有三种方式——金柱状 凸点,微柱,焊料凸点和各种裸芯片粘片方法。我们公司可以通过通信方式或是亲临现场方式帮助您选定最适合的装配方式。

通常来说先用一种方法做样板,然后另一种方法用于大批量生产比较可行。可以从板上直接贴装开始,当数量增加时,使用相同的设备转到微柱状或是倒装芯片方式。在每一个阶 段,客户都可以选择自己生产或是外包生产,也可以两种结合使用。

最后一点是客户需要意识到即将启动的无铅焊接以及它对装配工艺的影响。

建立装配线后,我们会培训您公司的员工如何处理裸芯片,检查,装配和任意数量的键合。同时也会协助在裸芯片采购和应用注意事项方面做书面记录,数据查证的详细规范。我

们的专业人士可以对整个流程由始至终做出详细说明,提供全程咨询,并根据需要培训设备操作。

我们的服务物超所值——如果是已和我们签订所有相关裸芯片的供货协议书,我们以通讯方式提供帮助将完全免费。如果是现场咨询服务,每天收费1500美金,外加差旅费。当然 这些费用也可以通过与我们签订大批量的裸芯片订单来摊销。

3. 成功案例

移动电话,膝上性便携产品和RFID应用都是最好的例子。Motorola公司最新的电话产品通过使用倒装片,节省15%以上的元件成本和20%的装配成本。中国的Sun Rise公司生产相 似规格的移动电话彩屏显卡。最初的黑百显卡使用Phillips LCD裸芯片驱动器,需要720个键合点,应用常规的板上直接贴装技术可以实现。到彩屏显卡时需要的LCD驱动器有940个 键合点,如果不大量增加芯片尺寸和电路板面积,芯片的周边根本容纳不下这么多的键合点。通过建立带金凸点的倒装芯片生产线,我们可以将键合点放在芯片中央。应用这种方 法不仅降低芯片成本同时节省80%的装配时间,因为只需要将裸芯片固定在一片箔片上而无需焊接。三千万个彩屏显卡每年节省的成本是非常可观的。

4. 技术方面的优势(由国家半导体提供)

电气性能

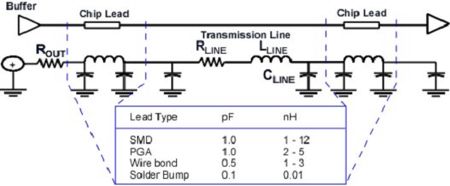

裸芯片较低的电感电容在模拟,RF和电源应用方面非常重要。信号传播和电源接地分配也得到改善。

电路连接引线的长度缩短和焊料凸点产生更低的寄生电感和电容。芯片间的更小距离可以提高响应速度上升沿时间,更小功率的驱动器也能改善响应上升沿时间。

尺寸和重量

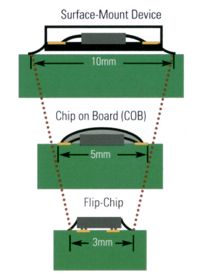

有空间限制的系统设计都会面对挑战,即如何同时将扩展功能需求,减小空间和降低成本同时兼顾到。对于很多手提便携式和其它小型产品来说,硅片外的包装已经成为排版布线 最主要的尺寸限制因素。把常规半导体封装产品转换成无封装的裸芯片,将给系统设计者提供有效利用有限空间同时减小高度和重量的机会。

裸芯片产品有两种装配方式:一是常用的是引线键合裸芯片,另一种是带凸点的倒装片裸芯片。两种装配形式都比传统封装芯片外形小很多。

如下图所示,使用常规的裸芯片可以使双向锁相环路的使用空间至少减少50%。

改进程度会随封装方法不同而不同,倒装片可以减少功能区域从70%到90%不等。

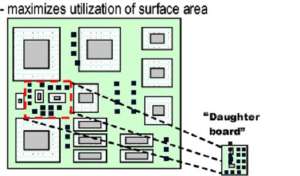

集成度的改善

随着尺寸缩小和基板间距改善,现有产品功能给设计者达成更高集成度提供了低成本,低风险的途径。与开发芯片级系统产品相比较,直接使用系统级封装中单个芯片的功能也可 能使设计时间缩短。

可靠性

应用裸芯片使互连结点数量减少从而大大提高可靠性。典型的封装器件每个I/O都有三个连接点,与之相比,引线键合的裸芯片只有两个结点,倒装片仅有一个焊接点。

典型的封装芯片内部连接

典型的板上直接贴装内部连接

典型的倒装片内部连接

| 购买人 | 会员级别 | 数量 | 属性 | 购买时间 |

|---|

邮编:518055

Copyright © 1992-2024

粤ICP备07034145号